T flip-flop. Çalışma prensibi, fonksiyonel diyagramlar

Tetikleyici, temsil eden en basit cihazdırdijital otomatik makine. İki kararlılık durumu vardır. Bu durumlardan birine "1" değeri ve diğer "0" değeri atanır. Cihazın durumu ve içinde saklanan ikili bilginin değeri, çıkış sinyalleri tarafından belirlenir: doğrudan ve ters. Mantıksal bir üniteye karşılık gelen ileri çıkışta bir potansiyel oluşturulduğunda, bu durumda tetikleme durumu tek olarak adlandırılır (ters çıktıdaki potansiyel mantıksal bir sıfıra karşılık gelir). Doğrudan çıkışta potansiyel yoksa, tetikleyicinin durumu sıfır olarak adlandırılır.

Tetikleyicileri aşağıdaki şekillerde sınıflandırın:

1. Kayıtlı bilgi yöntemiyle (asenkron ve senkron).

2. Bilgi yönetimi yöntemiyle (istatistiksel, dinamik, tek aşamalı, çok aşamalı).

3. Mantıksal bağlantıların gerçekleştirilmesi yoluyla (JK-flip-flop, RS-flip-flop, T-flip-flop, D-flip-flop ve diğer tipler).

Her tip tetikleyicinin ana parametreleri şunlardır: giriş sinyalinin maksimum süresi, tetiğin değiştirilmesi için gerekli olan zaman gecikmesi ve ayrıca tepki süresine izin verilmesi.

Bu yazıda, bu tür bir cihaz hakkında konuşalım.olarak - T-tetikleyici. Bu tür tetikleyiciler, sayılabilir bir girdi olarak adlandırılan sadece bir bilgi (T) girişine sahiptir. Her kontrol sinyalinin sayma (T) girişini aldıktan sonra durumunu ve durumunu değiştirir.

Geçiş tablosuna göre, yasaBu tür tetikleyicilerin işlevi, karakteristik denklem tarafından açıklanmaktadır: Q (t + 1) = TtQ "t VT'tQt. Denklemden, mantık sıfırı girişe (T) geldiğinde, T- tersine dönecek.

| St | Tt | S(t + 1) |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

T-flip-flop'un gerçekleştirdiği tablodan görülebilir.Ekleme işlemi, bu tür bir tetikleyicinin adının sayılabilir olmasına neden olmuş, onun bilgisi (T) girişi sayılabilir bir girdidir. Böyle bir tetikleyicinin girişindeki sinyal seviyesi, çıkışında (Q) olduğu gibi iki kat daha fazla görünür. Buna göre, T-flip-flop bir frekans bölücü olarak kullanılır.

Asenkron tipin bir T-tetikleyicisi olabilirilave bağlantılara sahip iki aşamalı bir RS flip-flopu temel alınarak oluşturulur: flip-flop (Q) çıkışı girişe (R) ve çıkışa (Q ') girişe (S) bağlanmalıdır. Bilgi girişi (T) senkron giriş (C) olacaktır.

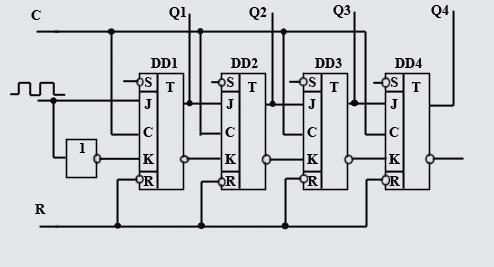

Fotoğraf bir T-tetikleyiciyi göstermektedir. İşlevsel şema.

Bilgi girişlerinde başlangıç durumundaVe-NO eleman ikinci flip-flop girişine, bir mantık bir seviye üretecek çünkü tetikleme birinci kalıcı bir kopya durumu meydana edilen mantıklı sıfır sayacı (T) girişine uygulanır (R ve S) beslenen mantık sıfır düzeyi, ikinci bir çevirme-flop flip-flop. Eğer T-flip-flop birleşme durumundaysa, o zaman girişler (R ve S) sırasıyla sıfır ve birlik seviyeleri ile beslenecektir. İlk sinyal, mantıksal olana eşit olan sayım girişine ulaştığında, mantıksal birim ilk tetikleyiciye yazılır. İkinci tetikleyicinin durumu değişmez, çünkü AND geçidinin çıkışındaki sıfır seviyesi durumunu engellemez. Sayım darbesi çıkarıldıktan sonra, giriş (T) sıfıra ayarlanır ve ikinci tetikleyici mantıksal olana geçer.

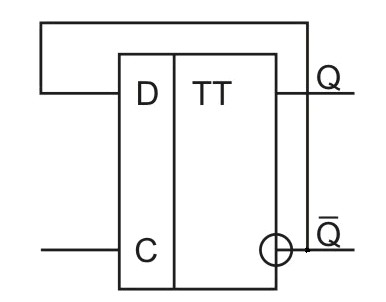

Fotoğrafta senkron T-tetik var. İşlevsel şema.

Senkronize t-flip-floplar, gerektiğinde T flip-flop girişinde bir mantıksal birim dizisinin potansiyelini temsil etmek için kullanılır.